在數碼3C產品日新月異的今天,當我們享受著智能手機流暢的操作體驗、筆記本電腦強大的計算能力、智能家居設備便捷的互聯功能時,很少有人會思考這些產品背后的核心技術——集成電路設計。這塊小小的芯片,承載著一個龐大而復雜的系統工程,堪稱現代電子產品的"大腦"。

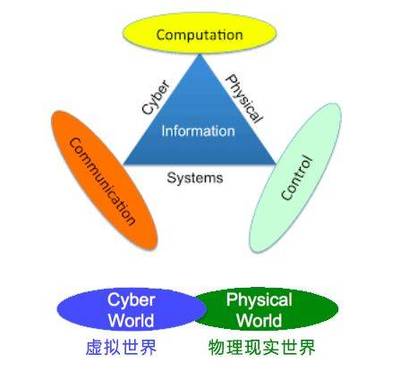

集成電路設計,簡單來說就是將數百萬甚至數十億個晶體管及其互連線路集成在微小的半導體芯片上,實現特定功能的過程。這個過程涉及物理、化學、材料科學、電子工程、計算機科學等多個學科的交叉融合,是現代高科技產業的集大成者。

集成電路設計的層次與流程

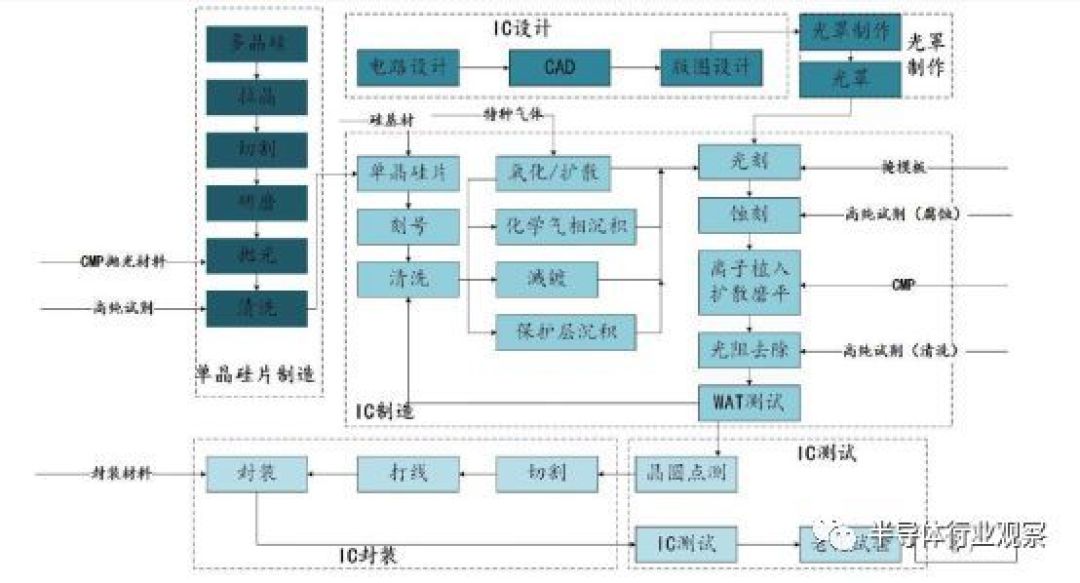

集成電路設計通常分為三個主要層次:系統級設計、邏輯級設計和物理級設計。

系統級設計是最高層次的設計,主要確定芯片的功能規格、性能指標和整體架構。在這個階段,工程師需要深入理解市場需求,將產品功能轉化為技術指標,并確定芯片的總體架構。

邏輯級設計是將系統級設計轉化為具體的邏輯電路。這個階段包括寄存器傳輸級設計和邏輯綜合,工程師使用硬件描述語言(如Verilog或VHDL)來描述電路的功能,然后通過邏輯綜合工具將高級描述轉化為門級網表。

物理級設計是將邏輯設計轉化為實際的版圖設計。這個過程包括布局規劃、單元布置、時鐘樹綜合、布線等步驟,需要考慮時序、功耗、面積、信號完整性等多種因素。

設計工具與EDA軟件

現代集成電路設計離不開電子設計自動化工具的支持。EDA軟件貫穿設計的全過程,包括:

- 設計與驗證工具:用于電路設計、仿真和驗證

- 綜合工具:將高級描述轉化為門級網表

- 布局布線工具:完成物理設計

- 時序分析工具:確保電路滿足時序要求

- 功耗分析工具:優化芯片功耗

- 可制造性設計工具:確保芯片能夠被成功制造

設計挑戰與技術突破

隨著工藝節點的不斷縮小,集成電路設計面臨著前所未有的挑戰:

- 物理效應問題:在納米尺度下,量子效應、寄生效應等物理現象變得更加顯著

- 功耗問題:芯片功耗密度持續上升,散熱成為瓶頸

- 時序收斂問題:時鐘頻率提高導致時序收斂更加困難

- 設計復雜度問題:晶體管數量激增,設計驗證工作量呈指數級增長

- 制造成本問題:先進工藝研發和制造成本持續攀升

為應對這些挑戰,業界不斷推出創新技術:

- 先進封裝技術:如2.5D/3D封裝、chiplet技術

- 新器件結構:如FinFET、GAA晶體管

- 新材料應用:高k金屬柵、鈷互連等

- 設計方法學創新:基于平臺的設計、IP復用等

產業鏈協同與生態建設

集成電路設計不是孤立的環節,而是整個產業鏈的重要一環。設計公司需要與晶圓代工廠、封裝測試廠、EDA工具供應商、IP供應商等緊密合作。這種合作不僅體現在技術層面,還包括標準制定、生態建設等多個方面。

IP核的復用是現代集成電路設計的重要特征。通過使用經過驗證的IP核,設計公司可以大幅縮短開發周期,降低設計風險。成熟的IP生態系統包括處理器核、接口IP、模擬IP等多個類別。

未來發展趨勢

集成電路設計將朝著以下幾個方向發展:

- 異構集成:將不同工藝、不同功能的芯片通過先進封裝技術集成在一起

- 智能化設計:引入人工智能技術輔助設計決策和優化

- 領域專用架構:針對特定應用場景優化芯片架構

- 安全性設計:從設計階段就考慮芯片的安全性和可信性

- 可持續發展:注重能效優化和環境友好型設計

結語

集成電路設計作為數碼3C產品的核心技術,其復雜程度和技術含量遠超常人想象。從概念到產品,需要經歷漫長的研發過程和嚴格的質量控制。正是這些看不見的設計工作,支撐著我們日常生活中每一個智能設備的正常運行。隨著技術的不斷進步,集成電路設計必將在推動數字經濟發展、促進社會進步方面發揮更加重要的作用。